# Digital Technical Journal

Digital Equipment Corporation

Volume 2 Number 4 Fall 1990

**Editorial** Jane C. Blake, Editor Barbara Lindmark, Associate Editor

**Circulation** Catherine M. Phillips, Administrator Suzanne J. Babineau, Secretary

**Production** Helen L. Patterson, Production Editor Nancy Jones, Typographer Peter Woodbury, Illustrator and Designer

Advisory Board Samuel H. Fuller, Chairman Richard W. Beane Robert M. Glorioso John W. McCredie Mahendra R. Patel F. Grant Saviers Robert K. Spitz Victor A. Vyssotsky

The *Digital Technical Journal* is published quarterly by Digital Equipment Corporation, 146 Main Street MLO1-3/B68, Maynard, Massachusetts 01754-2571. Subscriptions to the Journal are \$40.00 for four issues and must be prepaid in U.S. funds. University and college professors and Ph.D. students in the electrical engineering and computer science fields receive complimentary subscriptions upon request. Orders, inquiries, and address changes should be sent to The *Digital Technical Journal* at the published-by address. Inquiries can also be sent electronically to DTJ@CRL.DEC.COM. Single copies and back issues are available for \$16.00 each from Digital Press of Digital Equipment Corporation, 12 Crosby Drive, Bedford, MA 01730-1493.

Digital employees may send subscription orders on the ENET to RDVAX::JOURNAL or by interoffice mail to mailstop MLO1-3/B68. Orders should include badge number, cost center, site location code and address. U.S. engineers in Engineering and Manufacturing receive complimentary subscriptions; engineers in these organizations in countries outside the U.S. should contact the Journal office to receive their complimentary subscriptions. All employees must advise of changes of address.

Comments on the content of any paper are welcomed and may be sent to the editor at the published-by or network address.

Copyright © 1990 Digital Equipment Corporation. Copying without fee is permitted provided that such copies are made for use in educational institutions by faculty members and are not distributed for commercial advantage. Abstracting with credit of Digital Equipment Corporation's authorship is permitted. All rights reserved.

The information in this Journal is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this Journal.

#### ISSN 0898-901X

Documentation Number EY-E762E-DP

The following are trademarks of Digital Equipment Corporation: CI, DECsystem-10, DECSYSTEM-20, Digital, the Digital logo, HDSC, MCU, MicroVAX, NI, PDP-1, ULTRIX, VAX, VAX-11/780, VAX 6000, VAX 8000, VAX 8600, VAX 8650, VAX 9000, VAXBI, VMS, XMI.

IBM is a registered trademark of International Business Machines Corporation.

Kapton is a trademark of E. I. duPont de Nemours & Company.

MOSAIC III is a trademark of Motorola Corporation.

Micromaster Plus is a registered trademark of LTX Company.

Book production was done by Digital's Educational Services Media Communications Group in Bedford, MA.

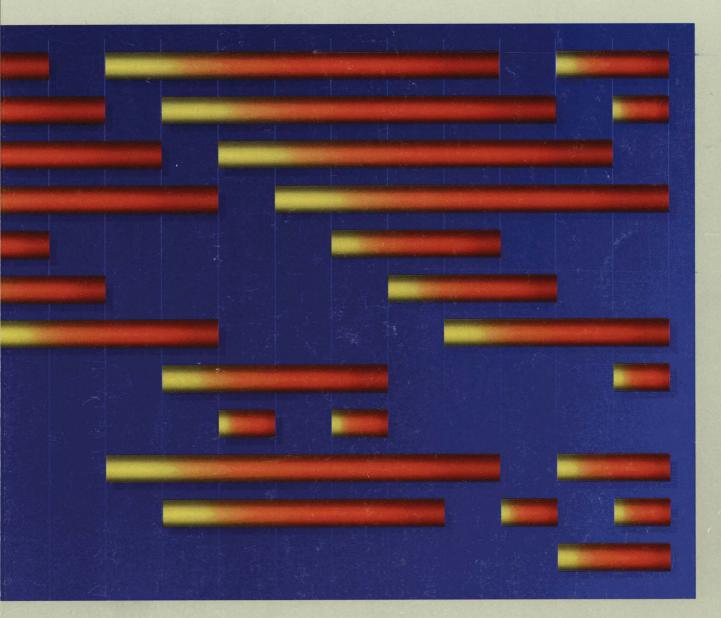

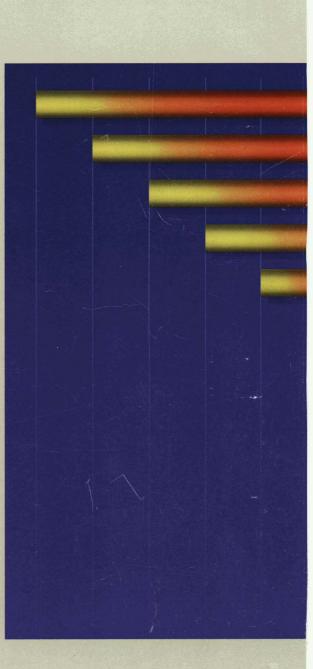

#### Cover Design

Digital's VAX 9000 mainframe system is the theme of this issue. Our cover depicts several simple instructions flowing through the VAX 9000 instruction execution pipeline. High performance was achieved by breaking the VAX instructions into small simple tasks that could be pipelined efficiently. Concurrent operation on up to six instructions simultaneously resulted in a execution rate of one simple VAX instruction per clock period.

*Gloria Monroy of the High Performance Systems Group designed the cover graphic, which was implemented in cooperation with David Comberg of the Corporate Design Group.*

# Contents

#### 11 Foreword

Carl S. Gibson

VAX 9000 Series

- 13 **Design Strategy for the VAX 9000 System** David B. Fite Jr., Tryggve Fossum, and Dwight Manley

- 25 VAX Instructions That Illustrate the Architectural Features of the VAX 9000 CPU John E. Murray, Ricky C. Hetherington, and Ronald M. Salett

- 43 *Semiconductor Technology in a High-performance VAX System* Matthew J. Adiletta, Richard L. Doucette, John H. Hackenberg, Dale H. Leuthold, and Dennis M. Litwinetz

- 61 *Vector Processing on the VAX 9000 System* Richard A. Brunner, Dileep P. Bhandarkar, Francis X. McKeen, Bimal Patel, William J. Rogers Jr., and Gregory L. Yoder

- 80 *HDSC and Multichip Unit Design and Manufacture* Peter B. Dunbeck, Richard J. Dischler, James B. McElroy, and Frank J. Swiatowiec

- 90 *The VAX 9000 Service Processor Unit* Matthew S. Goldman, Paul H. Dormitzer, and Paul A. Leveille

- 102 *The Unique Features of the VAX 9000 Power System Design* Derrick J. Chin, Barry G. Brown, Charles F. Butala, Luke L. Chang, Steven J. Chenetz, Gerald E. Cotter, Brian T. Lynch, Thiagarajan Natarajan, and Leonard J. Salafia

- 118 *Synthesis in the CAD System Used to Design the VAX 9000 System* Donald F. Hooper and John C. Eck

- Hierarchical Fault Detection and Isolation Strategy for the VAX 9000 System

Karen E. Barnard and Robert P. Harokopus

### Editor's Introduction

Jane C. Blake Editor

The VAX 9000, Digital's first mainframe computer, is the topic of papers in this issue of the *Digital Technical Journal*. As engineers writing for this issue relate, the primary goal of the project from the initial product strategy through manufacture was to design and build a very high-performance, highly reliable VAX system.

Design engineers applied both CISC and RISC techniques to achieve high levels of performance for this tightly coupled multiprocessor system. In the opening paper, Dave Fite, Tryggve Fossum, and Dwight Manley explain the strategy behind the design. They begin with an overview of the system, the technology, and CAD tools, and then describe the redesign of VAX instructions into small tasks which can be efficiently pipelined. The authors also touch upon three additional aspects of the VAX 9000 system: the integration of vector processing into the VAX architecture, new error handling techniques, and performance modeling.

One measure of performance is the number of instructions processed per cycle. The average number of cycles per instruction is less than five, which is nearly half the instruction execution rate of previous VAX systems. To illustrate the architectural features that enable this level of performance, John Murray, Rick Hetherington, and Ron Salett have selected a small sample of VAX instructions. They describe the instruction flow through the pipeline, how instruction features combine to work on a single macro, and how stages of the pipeline interact.

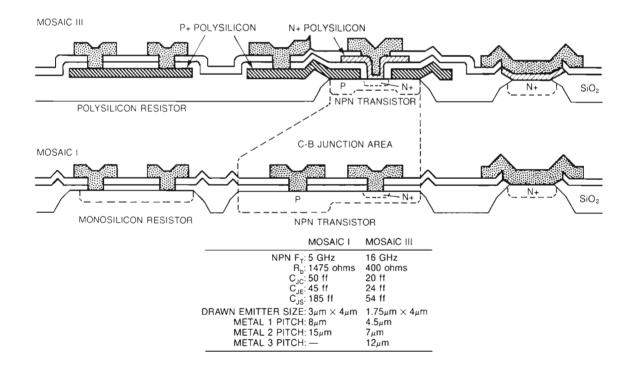

In addition to the architectural improvements, machine performance is enhanced at the semiconductor level by a new generation of semicustom and custom integrated circuits that support a low cycle time. Matt Adiletta, Dick Doucette, John Hackenberg, Dale Leuthold, and Dennis Litwinetz give an overview of the bipolar technology used in the system. They then describe the methods used to implement the 77 different gate array chips, the five custom chips, and the self-timed RAM architecture.

An additional performance improvement for numeric computations is the VAX vector architecture and is treated in the paper by Rich Brunner, Dileep Bhandarkar, Frank McKeen, Bimal Patel, Bill Rogers, and Greg Yoder. They discuss the architectural model and particulars of the VAX 9000 implementation, which affords numerically intensive applications performance four to five times greater than can be achieved by the scalar processor.

To ensure that the system performance gains at the semiconductor level were not diminished but were instead enhanced by packaging and interconnects, engineers developed several technologies unique in the industry. The technology behind the high-density signal carrier and the multichip unit are explained in the paper by Pete Dunbeck, Rich Dischler, Jim McElroy, and Frank Swiatowiec.

Equally important to performance in the new 9000 is system reliability as evidenced by the introduction of the service processor unit. In their paper about the service processor, Matt Goldman, Paul Dormitzer, and Paul Leveille relate how the MicroVAX-based system embedded within the 9000 detects, isolates, and corrects problems without interrupting the system.

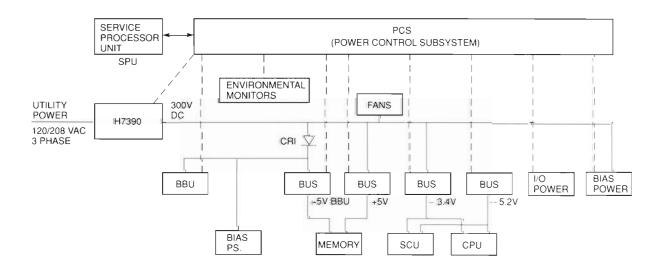

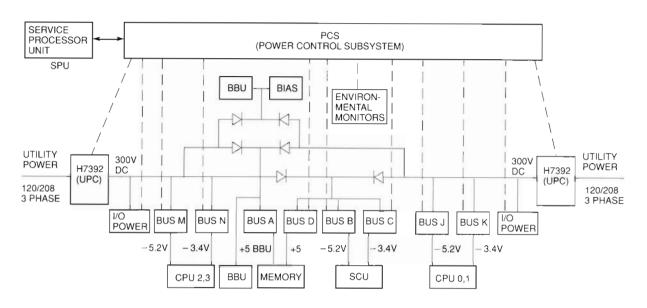

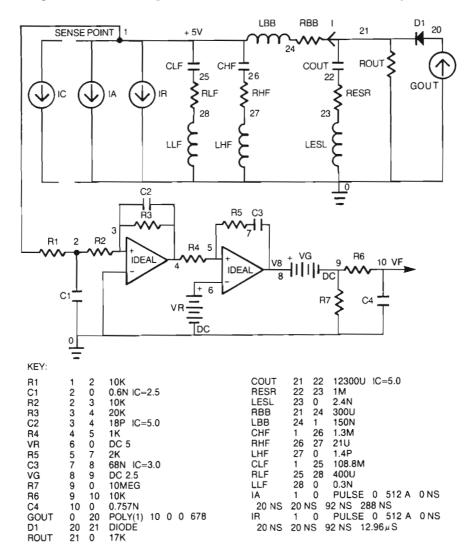

High system availability was also one impetus in the design of the power system. Some of the unique features of the power system, such as redundant regulators, improved load sharing and simulation, are discussed by Derrick Chin, Barry Brown, Charles Butala, Luke Chang, Steve Chenetz, Jerry Cotter, Brian Lynch, Raj Natarajan, and Len Salafia.

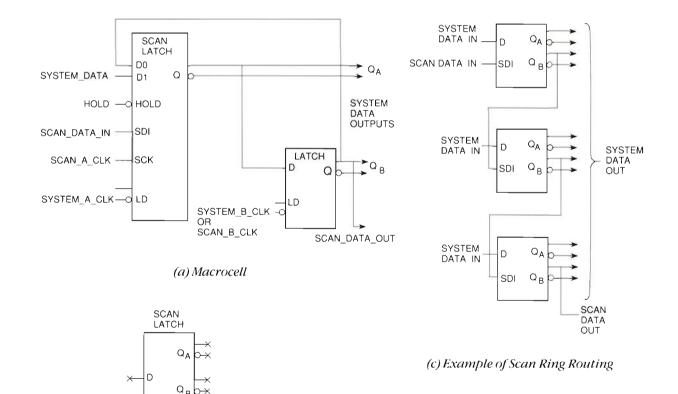

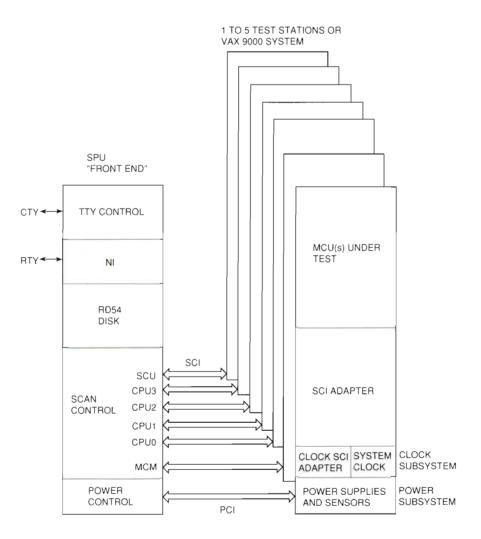

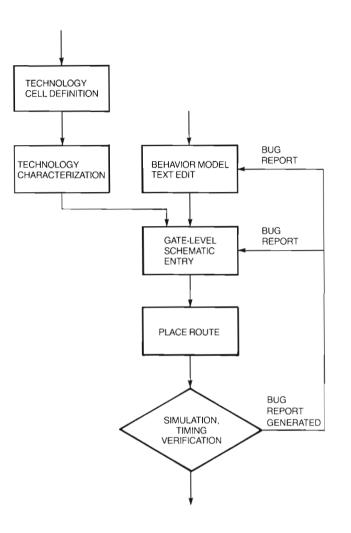

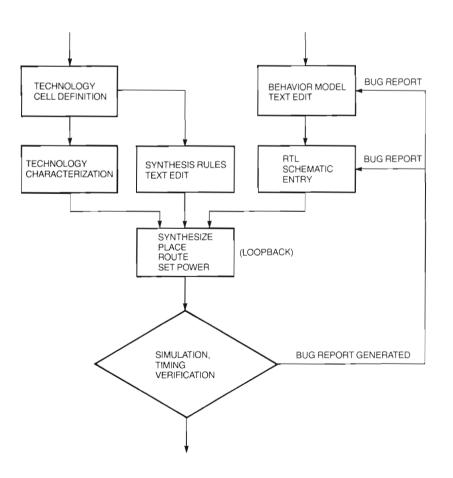

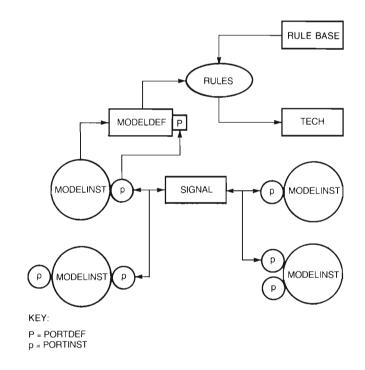

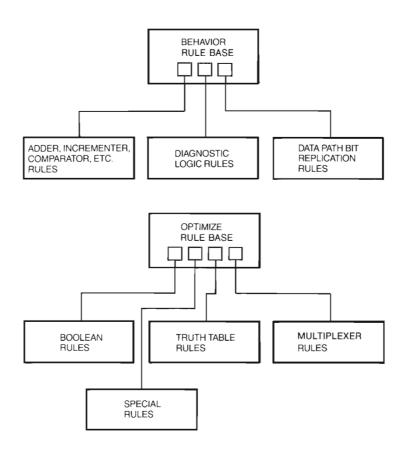

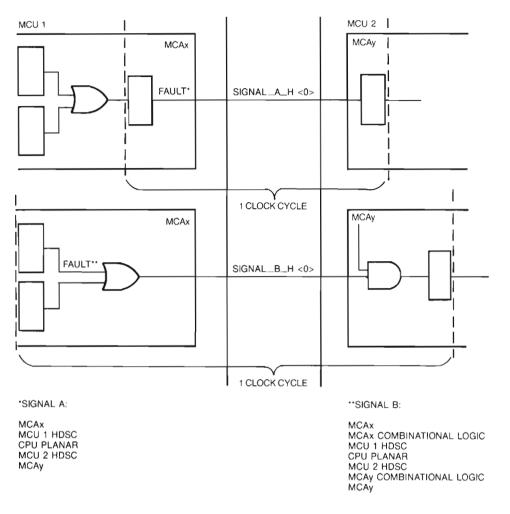

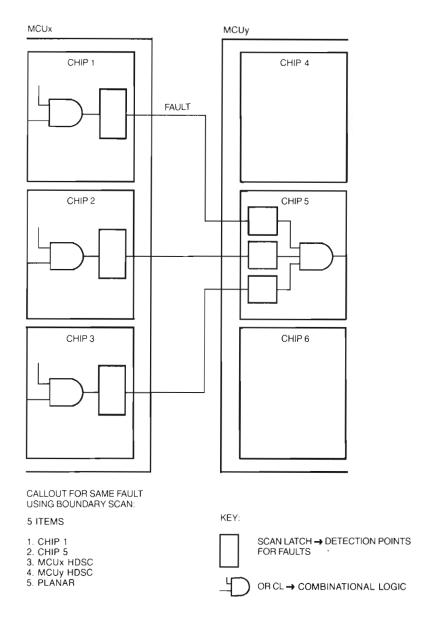

The two papers that close this issue address the topics of CAD methodology and system diagnosis. Don Hooper and John Eck describe a CAD methodology that combines advanced rule-based AI techniques with an object-oriented database. The new methodology saves logic designers significant time and reduces errors. A complex system such as the VAX 9000 requires improved system diagnosis capabilities to achieve the desired high system availability. Karen Barnard and Bob Harokopus demonstrate how a new scan system, in combination with scan pattern testing, and symptom-directed diagnosis achieve this necessary diagnosis capability.

The editors thank Rick Hetherington of the High Performance Systems Group for not only writing a paper but for his help in coordinating this issue.

Jane Blake

2

## **Biographies**

**Matthew J. Adiletta** Matthew Adiletta is currently contributing to the implementation of a new processor architecture and performing a technology evaluation to determine the technology for the implementation. He joined Digital in 1985 to work on a high-performance RISC architecture. Matt was not only the architect for the VAX 9000 system, but he also implemented the integer and floating point multiply and divide units and developed an ECL custom chip process. He holds one patent and has several patents pending. Matt received a B.S.E.E. (honors, 1985) from the University of Connecticut.

**Karen E. Barnard** A senior software engineer with the High Power Business Unit CPU Development Group, Karen Barnard wrote the read-only memorybased diagnostic for the VAX 9000 service processor unit's scan control module and developed the scan pattern diagnostic for the VAX 9000 CPU and SCU. Karen also worked on the debugging structural test process for the VAX 9000 kernel environment. Prior to joining Digital in 1986, Karen was with Data General Corporation. She received a B.S. (1983) in computer science from the Worcester Polytechnical Institute.

**Dileep P. Bhandarkar** As technical director for RISC systems, Dileep Bhandarkar is responsible for leading the architectural direction of RISC products. He joined Digital in 1978 and was responsible for managing the evolution of the VAX architecture. Dileep was the chief architect for VAX vector processing and coarchitect of Digital's RISC architecture. He holds one patent for his work at Digital and has several patents pending. His degrees in electrical engineering include a Bachelor of Technology from the Indian Institute of Technology and an M.S. and a Ph.D. from Carnegie-Mellon University.

**Barry G. Brown** The concept of designing DC-to-DC converters as system elements rather than individual "power supplies" was introduced into the high-power systems products by Barry Brown. He created and developed a highly flexible, high-reliability DC-to-DC conversion system for the VAX 9000 series. Barry designed, implemented, and verified the power system for the VAX 9000 Model 200 systems. He was a principal engineer for the Codex Corporation before coming to Digital in 1984. Barry is a graduate of Woolwich Polytechnic and Harlow Technical College.

#### Biographies

**Richard A. Brunner** As a principal engineer, Richard Brunner is the architect currently responsible for the engineering refinement and control of both the VAX and VAX vector architectures. He is the editor of the *VAX Architecture Reference Manual* and coauthor of the *VAX Vector Handbook* and several papers on the VAX vector architecture. He received a B.S. (high honors, 1984) in electrical engineering from Case Western Reserve University and an M.S. (1987) in computer engineering from Rensselaer Polytechnic Institute. He is a member of IEEE and Tau Beta Pi.

**Charles F. Butala** Presently responsible for the power system design and architecture of the VAX 9000 Model 400 systems, Charles Butala is a consulting engineer in the Information Systems Business Unit Power Systems Group. Since he joined Digital in 1976, he has been responsible for several power system design projects, including the VAX 8600 system. He is a member of IEEE and Tau Beta Pi, and holds honorary society membership in Eta Kappa Nu. Charles received a B.S.E.E. (1968) from Illinois Institute of Technology and an M.S.E.E. from Northeastern University.

**Luke L. Chang** After receiving his M.S. in electrical engineering from Virginia Polytechnic Institute and State University in 1988, Luke Chang joined the Power Systems Technology and Regulations Group. He is currently a hardware engineer and is responsible for developing simulation tools to perform high-quality software design verification tests for the next generation DC-to-DC power converters. Luke's previous responsibilities include transient analysis and testing of the VAX 9000 memory power distribution system, and power system cost reduction studies.

**Steven J. Chenetz** As a principal engineer in the Information Systems Business Unit Power Systems Group, Steven Chenetz is currently working on the H7390 for a high-power VAX system. He previously was a member of the design and development teams for the H7380 of the VAX 9000 system, the H7188 environmental monitoring module for the VAX 8600 power system, the VAX 8600 clock distribution system, and signal integrity for the VAX 8600 system. Steve joined Digital upon graduation from Rensselaer Polytechnic Institute in 1981. He has an M.S.E.E. from Northeastern University (1987).

**Derrick J. Chin** Derrick Chin is the engineering manager for several Information Systems Business Unit power groups and is design engineer of the VAX 9000 processor's DC power distribution system. His association with Digital began in 1961, and he has participated in many projects, from the PDP-1 and the DECsystem-10 to the VAX 8650 systems. His responsibilities have ranged from development of precision displays, circuit design, and core and semiconductor memories to environmental monitoring modules and power systems. He holds a B.S.E.E. (1959) from MIT.

**Gerald E. Cotter** Principal engineer Gerald Cotter is a member of the Information Systems Business Unit Power Systems Group. He was the project engineer and coarchitect of the VAX 9000 power control system (PCS). Jerry was the PCS interface to Customer Service and Support Engineering, Manufacturing, and Service Processor Unit Groups. He participated in development of the PCS and power system test strategies and the initial design of the T01060 power and environmental monitor modulc. His previous work includes the VAX 8600 system's power and control subsystem.

**Richard J. Dischler** In his position of systems engineer for the High Performance Systems Group, Richard Dischler worked on the VAX 9000 signal integrity project. He also was a member of the project team for the electrical design of HDSC and micropackaging for multichip units, planar boards, and connectors for the VAX 9000 system. Rich held similar responsibilities in the development of the VAX 8600 system. He joined Digital in 1982, and his previous experience was at Applied Research Laboratories. He holds a B.S.E.E. (1982) from Pennsylvania State University.

**Paul H. Dormitzer** As an undergraduate at Harvard University, Paul Dormitzer gained experience with the UNIX operating system by working as a programmer and operator. Upon receiving his B.A. in computer science in 1987, he joined Digital's High Performance Systems Group. He is currently an engineer in the High Performance Business Unit CPU Engineering Group. Paul's primary responsibilities are in the development of error recovery processes for high-power systems, such as the VAX 9000 system.

**Richard L. Doucette** Since joining Digital in 1979, Richard Doucette has been a member of several high-performance systems project teams. As a senior engineer on the VAX 8600 team, he helped introduce the Motorola Macrocell Array I (MCA1) technology into Digital and was responsible for its design analysis and characterization in the system. As engineering manager on the VAX 9000 team, he was responsible for the incorporation of MCA3 technology, custom chips, and self-timed RAM components in the system. He holds a B.S.E.E. (1973) from the University of Maine.

**Peter B. Dunbeck** Peter Dunbeck is an engineering manager in the High Performance Business Unit Technology Research and Engineering Group. He held various positions on the VAX 9000 program between 1985 and 1990, including technology program manager and design engineering manager for the multichip unit. Before joining Digital in 1984 as a manufacturing engineer, Peter developed energy conservation programs for Thermo Electron. He holds a B.S. (1977) in mechanical engineering from Virginia Tech and an S.M. (1979) in aeronautics and astronautics from MIT.

#### **Biographies**

**John C. Eck** The development of the majority of the physical design CAD tools used in the VAX 9000 system was managed by John Eck. He is a software engineer manager in the High Performance Systems CAD and Diagnostics Group. John was employed as the manager of the Automated Design Department of Badger Company before coming to Digital in 1984. He holds a B.S. (1964) in physics and an M.S. (1966) in aeronautics and astronautics from MIT, and an M.B.A. (highest honors, 1984) from Babson College.

**David B. Fite Jr.** Consultant engineer David Fite was a member of the initial architecture team for the VAX 9000 system. He developed the architecture for the branch prediction, instruction fetch, and instruction decode for the VAX 9000. His previous work includes responsibility for prototype debugging on the VAX 8600 system. Dave joined Digital in 1982. He has one patent and several patent applications pending. He is a graduate of Worcester Polytechnic Institute with a B.S. (honors) in electrical engineering.

**Tryggve Fossum** Tryggve Fossum is the system architect of the VAX 9000 system. He received a B.S. (1968) from the University of Oslo and earned his Ph.D. (1972) from the University of Illinois. Tryggve joined Digital in 1973 and worked on the design of high-end computers, notably the VAX-11/780 system. As a project leader on the VAX 8600 team, he guided the design of the floating point accelerator. He has also worked on several research projects, including an early raster scan graphics workstation, and a workstation with an integrated disk system.

**Matthew S. Goldman** As a senior engineer on the VAX 9000 project team, Matthew Goldman designed the scan control chip, which contains the control logic for the VAX 9000 scan system. He was also the responsible engineer for all VAX 9000 service processor hardware. Prior to joining Digital's High Performance Systems CPU Group in 1986, Matt was a design engineer for Raytheon Company. He is a member of Tau Beta Pi and Eta Kappa Nu. Matt holds a B.S. (highest honors, 1983) and an M.S. (1988) in electrical engineering from Worcester Polytechnic Institute.

**John H. Hackenberg** In 1968, John Hackenberg came to Digital as a technician on the KI-10 project, leaving after two years to serve in the armed forces. He returned to Digital in 1971 and worked on the designs for various high-end systems, including the KL-10. As a consulting engineer on the VAX 8600 project, he worked in the area of signal integrity. John was the project leader for the MCA3 gate array used in the VAX 9000 system and is currently developing a bipolar gate array. He holds a B.S.E.T. (1979) from the University of Lowell.

**Robert P. Harokopus** A cum laude graduate of the University of Michigan, Robert Harokopus received a B.S. (1986) in computer engineering and is now studying for an M.S. in computer engineering from Boston University. Bob is a senior software engineer and joined Digital in 1986. He developed the symptomdirected diagnosis software used in the VAX 9000 service processor unit. Bob also developed software for the HIDE CAD tool and SCEPTER automatic test pattern generator, both of which were used in the VAX 9000 design project. He is a member of Tau Beta Pi and Eta Kappa Nu.

**Ricky C. Hetherington** As a principal engineer with the High Performance Systems Group, Ricky Hetherington is currently the project leader of the translation buffer and cache design of the VAX 9000 system. He holds one patent and has several patents pending on the various design features of the VAX 9000 M-box. Rick joined Digital in 1982 as a senior engineer in Digital's Large Computer Group. He has a B.S. from Pennsylvania State University.

**Donald F. Hooper** Don Hooper is a consulting engineer in both logic design and CAD disciplines. He initiated and led the development of the Synthesis of Integral Design program, Digital's first synthesis tool. Before coming to Digital in 1979, he was architect for the Itel 7031 mainframe and cache designer for the Itel Advanced System 4. He is a graduate of Don Bosco Technical Institute. Don holds patents in speech recognition circuits, the tag and queuing system for Digital's first pipelined CPU, and the control storage pipe for the VAX 8600 system. In addition, he has several patents pending in logic synthesis.

**Dale H. Leuthold** A member of the technical staff of the Integral Circuit Design Group, Dale Leuthold led the design team for the VAX 9000 vector register chip. He is currently working on random-access memory development for high-speed mainframes. Dale was responsible for bipolar integrated circuit design at Signetics Corporation and Trilogy Systems Corporation before coming to Digital in 1986. He holds one patent and has one patent pending. Dale received a B.S. from Oregon State University.

**Paul A. Leveille** In his nearly ten-year relationship with Digital, Paul Leveille has specialized in the development of high-power systems, particularly the VAX 8600 and VAX 9000 systems. As a principal engineer in the High Performance Business Unit, he helped define the VAX 9000 service processor subsystem and was responsible for developing the scan control firmware and portions of the service processor application software. Paul's previous responsibilities include console diagnostics, firmware, and application software.

#### **Biographies**

**Dennis M. Litwinetz** The project leader for the design of four standard cell and custom chips for the VAX 9000, Dennis Litwinetz is a consulting engineer in the High Performance Business Unit. He has previously participated in the design of two standard cell chip designs for the VAX 8600 system. He joined Digital in 1967 as a technician for the DECsystem-10 Engineering Group. Dennis has a patent pending for the VAX 9000 self-timed register file design. He received a B.S.E.E.T. from Lowell Technological Institute and an M.S.C.E. from the University of Lowell.

**Brian T. Lynch** Brian Lynch is a principal hardware engineer in the Information Systems Business Unit Power Systems Group. In this position, he designed and developed the H7382 bias power supply used in the VAX 9000 system. He is presently working on power solutions for future high-performance systems. Prior to joining Digital in 1972, Brian was responsible for power converter and analog module design at Intronics. He has a B.S.E.E. (1978) from Worcester Polytechnic Institute.

**Dwight Manley** As a principal engineer on the VAX 9000 project, Dwight Manley was responsible for all of the performance modeling of the VAX 9000 CPU design. His present responsibilities include writing code for a Digital Extended Math Library product. Dwight joined Digital in 1979 as a member of the Systems Performance Analysis Group. Prior to that time, he worked as a systems programmer for the Bell Telephone System. Dwight has a B.S. (1971) in mathematics from the University of Massachusetts and an M.S. (1976) from Northeastern University.

**James B. McElroy** Jim McElroy is the multichip unit operations manager. His work on the VAX 9000 system began with interconnect and packaging, followed by the management of the physical technology efforts. He then became the manufacturing systems program manager for the introduction of the VAX 9000 system into manufacturing. Before joining Digital in 1976, Jim worked at RCA on packaging and interconnect design for military computer systems. He received a B.S.M.E. and an M.S.M.E. from Northeastern University.

**Francis X. McKeen** The project leader for the V-box unit of the VAX 9000 system was Francis McKeen. Prior to working on the VAX 9000 system, he wrote microcode for the VAX 8600 and VAX 8650 systems. Frank is a principal engineer and has been with Digital for seven years. He holds one patent and has several patent applications pending. Frank received a B.S.E.E. from Northeastern University and is a member of IEEE.

**John E. Murray** The coauthor of *Microarchitecture of the VAX 9000*, John Murray is a consulting engineer in the High Performance Business Unit. He served as project leader of the design team for the I-box unit of the VAX 9000. He joined Digital in 1982. John's previous employer was ICL in the United Kingdom, where he was a design engineer. He received a B.Sc. (1969) from Warwick University. He holds one patent and has several patents pending.

**Thiagarajan Natarajan** Thiagarajan Natarajan is manager of a DC-to-DC converter group in the Information Systems Business Unit. His group develops a high-density and highly reliable DC-to-DC converter, associated hybrids, semi-conductor components, and the distribution system for the next generation, high-performance VAX systems. Raj's prior experience includes positions at General Electric, Bell Laboratories, and Perkin Elmer Corporation. He has a Ph.D. in clectrical engineering, has been awarded one patent, and has authored approximately seventeen technical papers.

**Bimal Patel** Principal engineer Bimal Patel joined Digital in 1986 as a senior engineer. His primary responsibility since that time was the design of the V-box unit of the VAX 9000 system. Bimal was previously employed as a senior engineer in the CPU Design Group of Prime Computer, Inc. He has an M.S. in computer engineering from Boston University.

**William J. Rogers Jr.** William Rogers is an engineer in the VAX 9000 CPU Group, where he developed the design of the control logic of the V-box unit for the VAX 9000. Prior to working on this high-performance system, Bill was a member of the SASE Support Engineering Group. He joined Digital in 1986 and is a member of IEEE and Tau Beta Pi. He received a B.S. (1986) in electrical engineering from Michigan Technological University.

**Leonard J. Salafia** The development of the AC front end for the VAX 9000 system was the responsibility of Leonard Salafia, who is the manager of the AC Power Interface Development Group. His previous work at Digital includes supervising the development of storage system power products for the Central Power Supply Engineering Group and for the Storage Systems Power Group. Len worked for General Electric prior to coming to Digital in 1980. He holds a B.S.E.E. (magna cum laude, 1969) from the University of Hartford and an M.S.E.E. (1976) from Rensselaer Polytechnic Institute.

#### **Biographies**

**Ronald M. Salett** As a consulting engineer in the High Performance Systems Group, Ron Salett is currently leading the development of a new high-performance CPU. As a project leader for the VAX 9000 system, he was responsible for the architecture, design, and microcode of the execution unit. Since joining Digital in 1977, Ron has also worked as an architect and project leader on low-end integrated PDP-11 systems. He holds two patents. Ron holds a B.S.E.E. (1975) from Carnegie-Mellon University and an M.S.E.E. (1979) from Worcester Polytechnic Institute.

**Frank J. Swiatowiec** In 1988, Frank Swiatowiec became HDSC operations manager, with the primary responsibility to transition Digital's new HDSC technology to volume production. He was one of the engineering managers responsible for the definition and development of the HDSC. Frank had over 15 years of experience in the semiconductor industry when he joined Digital in 1986. While with Motorola Corporation, he was awarded four patents on ECL circuit designs. Frank holds a B.S.E.E. from the University of Illinois and an M.S.E.E. from Arizona State University.

**Gregory L. Yoder** Gregory Yoder is a senior hardware engineer with the High Performance Systems CPU Engineering Group. His primary responsibilities on the VAX 9000 system included the design and testing of the V-box unit, and prototype system debug, for which he received an excellence award. He also assisted Manufacturing in producing and installing external field test VAX 9000 machines. Greg joined Digital in 1988, after participating in a one-year co-op session at IBM. He holds a B.S.E.E. from Pennsylvania State University.

### Foreword

Carl S. Gibson VAX 9000 Program Manager

This issue of the *Digital Technical Journal* is a collection of papers describing the technologies, designs, and design methods employed in Digital's VAX 9000 mainframe/supercomputer, which was introduced in the fall of 1989.

The VAX 9000 system embodies hundreds of innovations in most areas of design, manufacture, and service. In selecting papers for this journal, we have attempted to reflect the immense scope and variety of this program, which ranks among the largest and most complex in the history of our industry.

In the summer of 1983, a small group of us set about to determine what it would take for Digital to develop a true mainframe. We felt that a mainframe VAX would be a powerful addition to Digital's product family. The products that we have created took form, changed, and evolved over the months and years as technical challenges yielded to innovations, rigor, and discipline. An undertaking on this scale necessarily undergoes numerous transitions as new data emerges, assumptions are tested, and alternatives are eliminated. Technical breakthroughs built upon one another incrementally as we pressed the design closer to our goals. The primary objectives of very high system-level performance and world-class reliability drove the design process and the changes that emerged.

The planar logic packaging is illustrative of how changes and improvements built upon one another. The reliability benefits of minimal connections precipitated a logic packaging design change from stacked modules in dual backplanes to the planar array. This change — an optimization for reliability — in the end actually helped performance and maintainability. Ultimately, though not envisioned at the time, the adoption of the planar array had a significant impact in that this structure enabled impingement air cooling and elimination of the bulky liquid system that was part of the initial design. The final design of the VAX 9000 system reflects, in myriad forms, this continual process of successive refinement toward shared goals.

Design changes notwithstanding, our primary strategy remained constant. The reader will note that, while we innovated aggressively in CPU structure, implementation technologies, and design methodologies, we preserved full compatibility with the VAX, Digital storage, and Digital networking and cluster architectures. We wanted Digital and our customers to be able to enjoy very high performance levels in a product that was compatible with prior investments. Therefore, we drew as much as possible from existing products and designs from many Digital development groups. As a result, the VAX 9000 system incorporates Digital's standard XMI bus and popular BI, CI, and NI system-level interconnects. The system runs VMS and ULTRIX operating systems, VAX layered products, and all of our customers' and independent software vendors' tools and applications. This capability proved especially rewarding when in the final months of the project, our own VAX 9000 prototypes, running our unmodified CAD tools, accelerated the processing of the inevitable lastminute changes.

High-performance computation fundamentally requires two key ingredients: short machine cycle times and maximum computational work performed in each cycle. The semiconductor and multichip unit papers describe how we minimized the VAX 9000 cycle time by use of fast circuits, highdensity packaging, and high-speed interconnects. These papers are complemented by architecture descriptions through which the authors present the innovative features that minimize the number of cycles required to execute the VAX instruction set. These papers present the sophisticated pipelining techniques and vector processing capabilities incorporated in the VAX 9000 system.

Equal in importance to the computational capabilities of the product are the service and control features of the system. Papers covering the VAX 9000 service processor and the system's fault management capabilities provide the reader with insights into these important aspects of the product.

The development strategy for the VAX 9000 system was explicitly formulated to deal with enormous technical and project complexity. Complex-

ity itself was the single most formidable challenge facing the team. Apparent from the outset, was the fact that such an ambitious product required the integration of a very large number of discrete design objects; each had to be conceived, created, documented, tested, and ultimately integrated and verified as part of the whole. The reader will see the diversity of these efforts and recognize the challenge of unifying a design from this breadth of technical advancement.

Central to our strategy was the creation of a unified design tool suite operating in a seamless, homogeneous VMS computing environment. The first few years of the project were devoted to construction of this environment in parallel with toplevel design formulation. The recognition that rigorous design methods were crucial to our success was possibly one of the team's most powerful fundamental notions. Papers included in this journal illustrate some of the legacy of powerful CAD tools and structured design approaches created by the VAX 9000 team.

As we have seen for the product, the methodologies were not immune to change as the project progressed. Working with rapidly evolving technologies, design process experts continually adapted to evolving user needs. Concurrent design permeated every aspect of the project and dominated the way people worked together, with many aspects of the technology and product design converging and adapting as we learned from our own processes. When the manufacturing process needed some help, designs could be reprocessed with the new rules and rereleased to keep things moving ahead.

And, move ahead they did! Today, the VAX 9000 system is installed at many customer sites where the systems are exceeding our original goals in both performance and dependability. It has been accepted by experienced, high-end computer users as a bona fide mainframe—a mainframe with the unique advantage of full integration with Digital's rich distributed processing architecture.

The VAX 9000 system was created by engineers working in many disciplines and collaborating worldwide to invent hardware, software, and processes that have significantly advanced the state of the art of computer design, manufacture, and service. The papers in this journal describe but a few representative examples of the creativity and determination of this large and dedicated team of professionals.

## Design Strategy for the VAX 9000 System

The VAX 9000 system is Digital's newest high-end processor in the VAX family. This paper describes the design strategy used to achieve high performance and shows how RISC concepts were applied to a CISC architecture. New opportunities for parallelism in VAX program execution were found by breaking the VAX instructions into simple tasks which could be pipelined efficiently. By using independent, dedicated pipeline stages, execution rates approach one instruction per cycle.

The task confronting the VAX 9000 design team was to develop a VAX system that outperformed any previous VAX system and that was competitive with similarly sized processors from other vendors. Although the VAX system is based on one of the world's most popular computer architectures, the VAX architecture's instruction complexities preclude efficient macroinstruction pipelining, such as that found in reduced instruction set computers (RISC). RISC processors can be built with low gate counts to handle simple, fixed-length instructions sets, load/store architectures, and delayed branching.

To compete with machines based on such architectures and still remain compatible with the VAX architecture, the design team chose to implement the VAX architecture on the VAX 9000 system by applying techniques that were similar to those used in RISC processors. We redesigned the VAX instructions into small, simple tasks, and designed dedicated hardware that was optimized for each task. The result is a network of specialized processors, each of which has its own data paths and state machines, that operate in parallel and execute VAX instructions quickly. The most common, simple instructions are executed at the rate of one per cycle.

#### System Overview

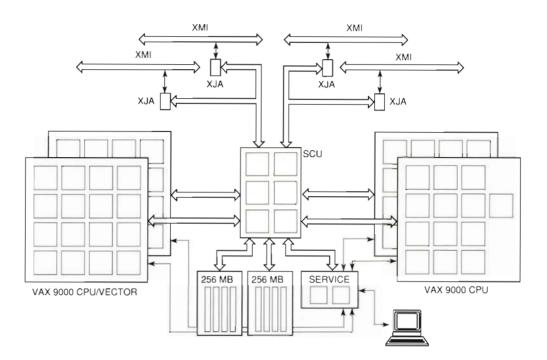

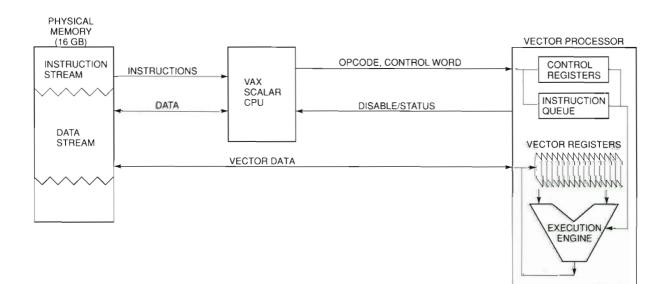

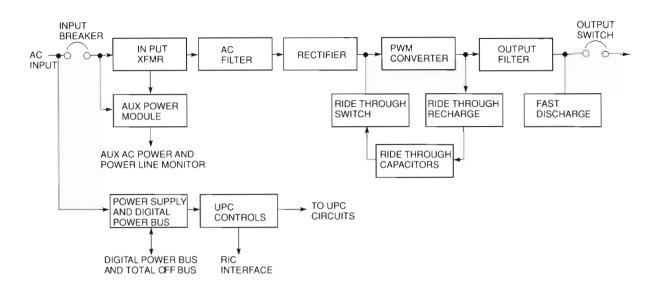

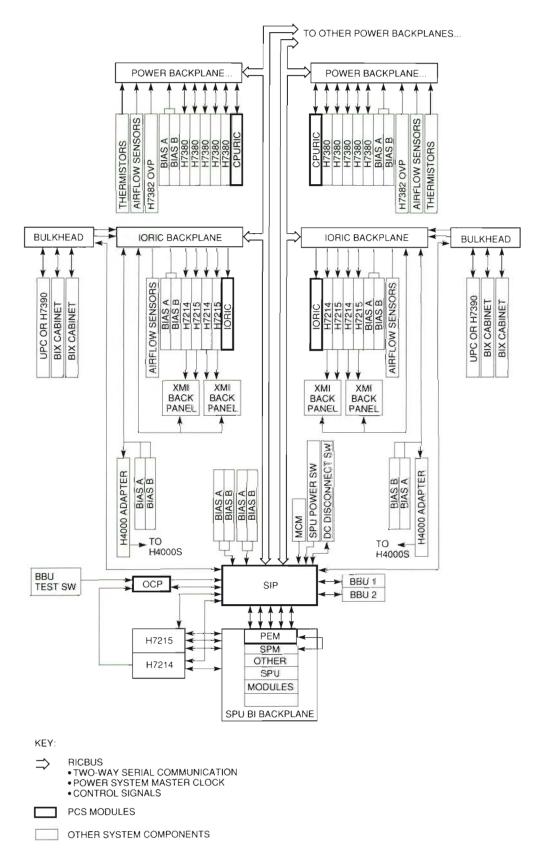

The VAX 9000 system is a tightly coupled multiprocessor, which runs the symmetric multiprocessing (SMP) version of the VMS operating system and can have up to four processors sharing a central main memory. Figure 1 shows a simplified block diagram of the system. The major system components include four CPUs, two memory controllers, two I/O controllers, and a service processor, which is connected through the system control unit (SCU). Through a cross-bar switch, the SCU provides highspeed, simultaneous transfers among the central processors, I/O devices, and memory banks. System cache consistency is maintained with duplicate tag directories located in the SCU. As references are made to memory, the addresses are checked against the tag directories. If a cache hit occurs, the cache in question is requested to invalidate or write back to main memory. The SCU supplies a bandwidth that allows near linear performance improvement as new processors are added to the system. The memory is interleaved on cache block boundaries to provide bandwidth for multiple CPUs and vector processors.

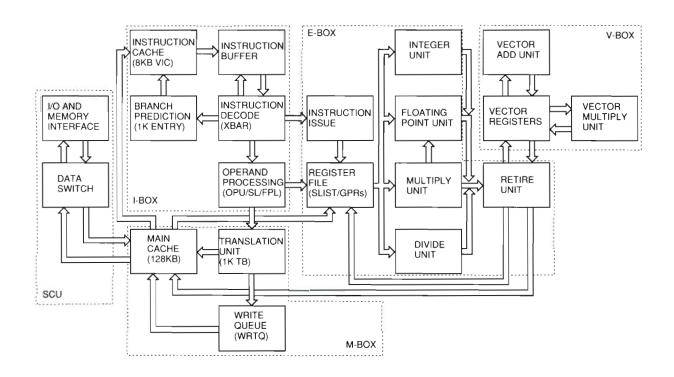

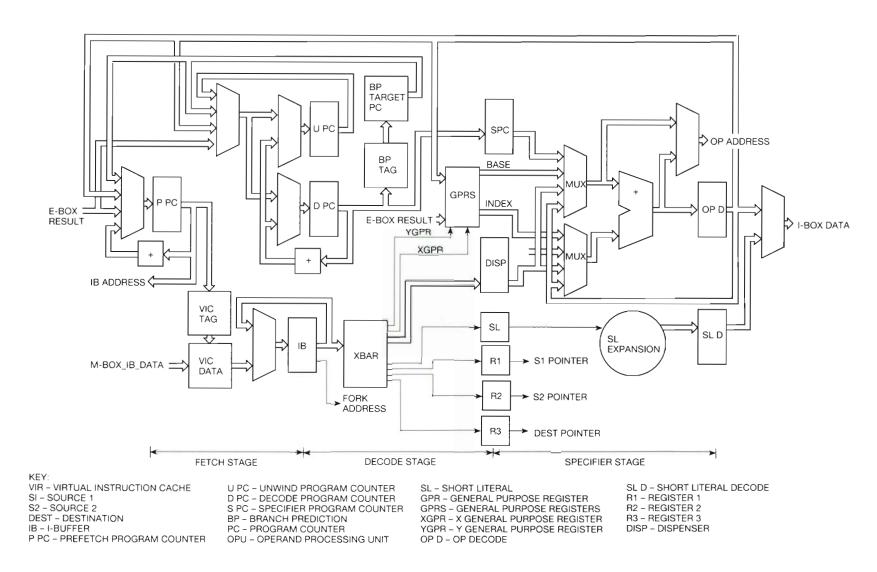

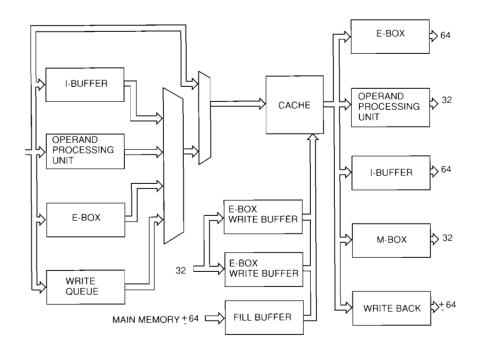

Four XMI backplane buses provide high bandwidth paths to I/O devices. Although the XMI is used as the system bus in VAX 6000 systems, the XMI is used exclusively for I/O in the VAX 9000 system. Several new adapters were designed to increase throughput and reduce latency for I/O transactions. These adapters include connections to the CI, the NI, the BI, and local disk controllers. Although highperformance I/O features, such as disk striping, solid-state disk, and load balancing have been added to all VAX systems, the VAX 9000 system benefits the most from these features because it has the I/O backplane bandwidth to take advantage of them. A block diagram of a single VAX 9000 CPU connected to the SCU and the major data paths between the two units is shown in Figure 2.<sup>1</sup>

#### Technology Contributions to Improved Performance

The central processor cycle time has been reduced to 16 nanoseconds (ns) mainly by the use of fast emitter-coupled logic (ECL) semiconductors and

Figure 1 VAX 9000 System Diagram

fast self-timed random-access memories (RAMs) for registers and caches, and by decreasing the interconnect wire length between components.

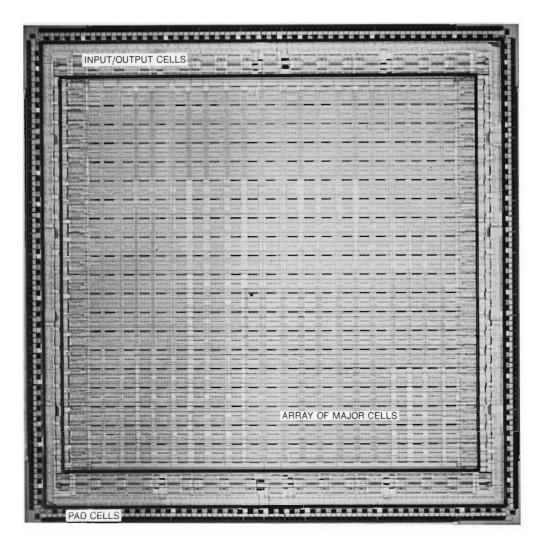

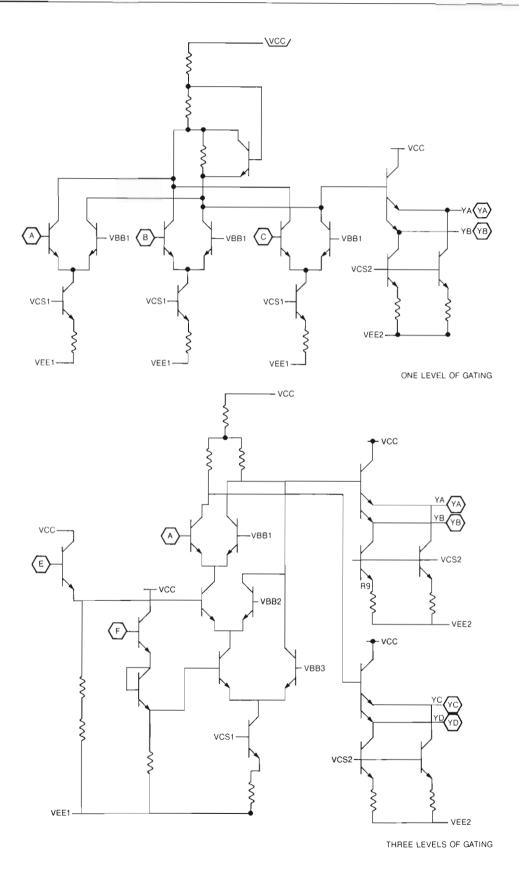

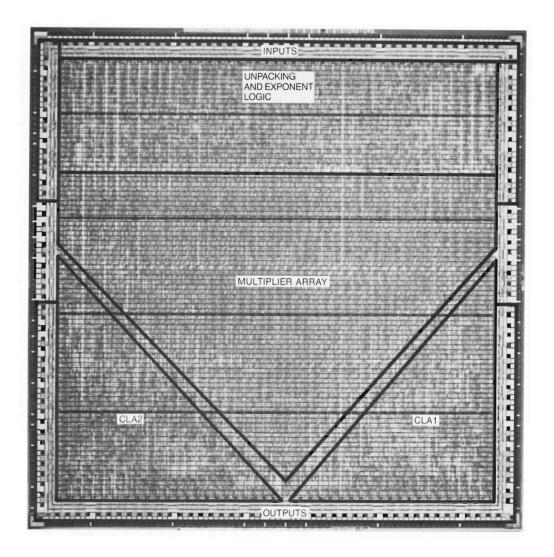

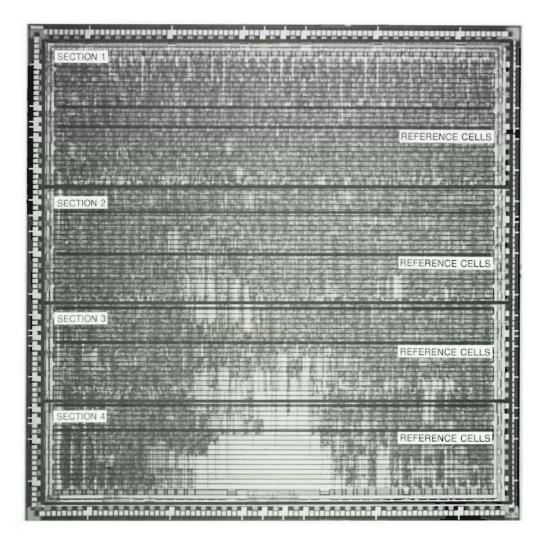

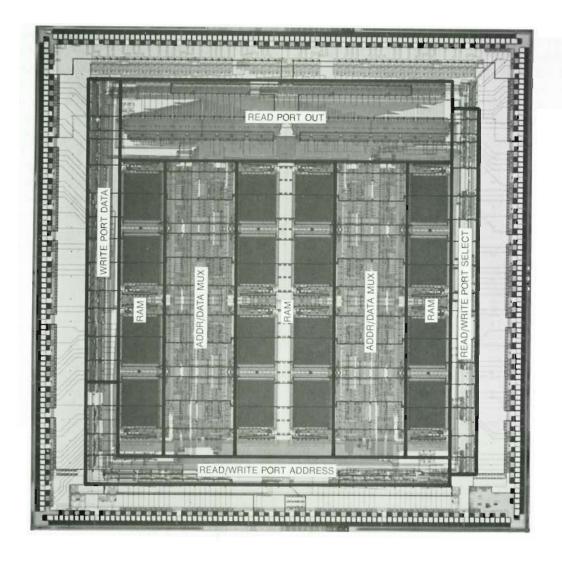

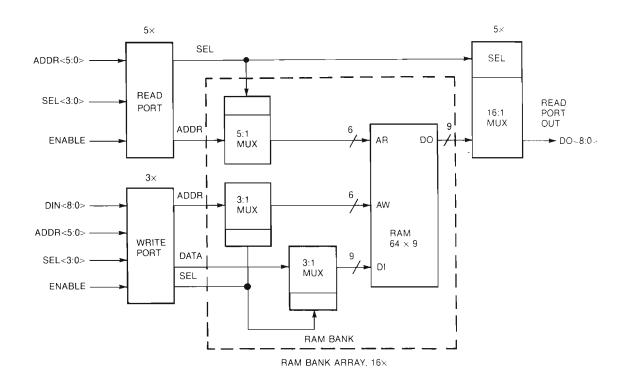

Motorola's Macrocell Array III (MCA3) technology provided both macrocell array and standard cell capabilities. The entire system is composed of 77 unique MCA3 options and 5 custom chip types. A single MCA3 contains 838 cells (414 major, 224 input, and 200 output), which yield 10,000 equivalent gates, and 256 1/O pins. Maximum power dissipation is 30.0 watts, with unloaded gate propagation delays of 120 picoseconds (ps). Performance-critical operations, such as multiplication, division, integer and vector register accesses, and system clocking, were further aided by employing custom chips.<sup>2</sup>

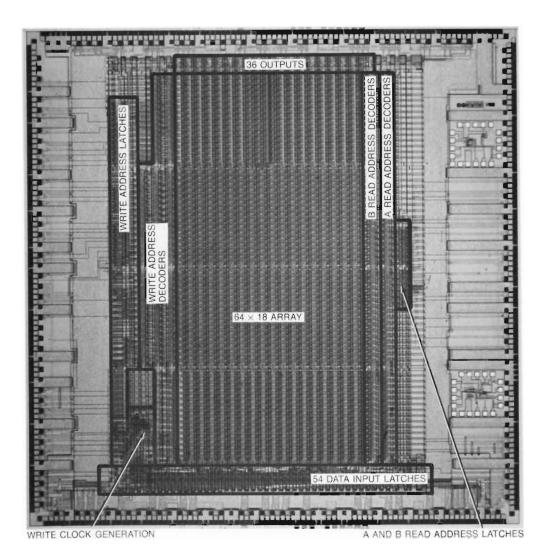

Caches for instruction stream and memory data, scratch pad registers, and control stores all require high-speed local storage. Two versions of a proprietary self-timed RAM were designed for these specific applications. A 4 kilobit (Kb) selftimed RAM, at 5.5 ns, and a 16Kb self-timed RAM, at 11.5 ns, provide internal input and output latches and write pulse generation circuitry. Multiple access modes allow highly pipelined operations to take advantage of shorter access times.

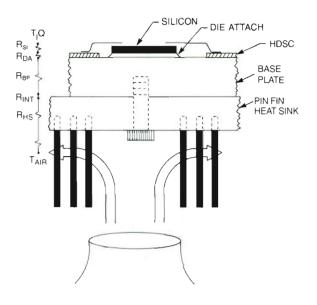

Each new semiconductor generation reduces cycle time, which increases the relative importance of interconnect delay. High density signal carriers (HDSC), tape automated bonding, and a single planar module all reduce the interconnect delay between active components in the VAX 9000 system. Strict impedance control is maintained throughout the system. Clock skew is minimized by employing fixed-length, differential transmission and dedicated routing layers.

#### CAD Contributions to Improved Performance

Hundreds of computer-aided design (CAD) tools were used during the design and construction of the VAX 9000 system. However, none of these tools was more important in improving performance than the physical layout and timing analysis tools. Once the design team had placed large functional sections, placement tools refined individual macrocell selection and pin placements. Over 33,000 pins were selected to minimize overall wire length and maximize critical interconnections.

Routing presented several challenges. All levels of interconnect included critical signals, differential pairs, and fixed-length requirements. The HDSC contains large cutouts that enable die attachment and allow cooling through the back panel. These large routing restrictions and special routing characteristics could not be handled by existing CAD tools. Therefore, we developed Chameleon, a general-purpose router. With Chameleon, crosstalk is minimized, and crossing counts are maintained and used to increase signal integrity, which improves performance.

To model the timing relationships within the system, we used sophisticated CAD tools to generate an accurate representation of the VAX 9000 system. Detailed timing models of each macrocell device were created using the SPICE simulator program.<sup>3</sup> Chameleon and signal integrity tools provided delay values for each signal within the MCA3, HDSC, and planar modules. CPUDLY, using the AUTODLY timing tool, tied the various pieces together and gave the design engineers a powerful view of the timing domain.

#### Instruction Processing

VAX systems exist in a variety of environments and run thousands of applications. With any new, highperformance VAX system, it is important to increase the speed of all applications and to continue to provide general-purpose computer power. Given the size of the installed VAX base and the nature of the applications, performance gains should not require code modifications. Digital has gathered substantial information on how VAX processors are used. This data formed the basis for design decisions and trade-offs we made in the development of the VAX 9000 system.

#### Simple Instructions

In many VAX programs, only a few opcodes are responsible for a large percentage of the instructions issued. Most of these opcodes are simple and limited to a single arithmetic or logical operation. Often, one of the operands is in memory. A typical example is

#### ADDL3 (R0),R1,R2

Because of the high frequency of these instructions, speeding up these instructions is a top priority. Most of the high performance achieved on RISC processors is derived because these instructions are pipelined. In a complex instruction set computer (CISC), such as a VAX system, pipelining macro-instructions is more complex. Therefore, previous VAX implementations have pipelined operations at the microinstruction level.<sup>4</sup>

Processing simple instructions in a VAX system involves obtaining and decoding the instruction, fetching source operands, performing an operation, and storing the result. The most important

Figure 2 VAX 9000 CPU/Vector Block Diagram

difference between the way a VAX processor and a RISC processor process simple instructions is how the variable length instructions and memory specifiers are handled. VAX operands may reside in general-purpose registers (similar to RISC operands), in memory, or may be embedded in the instruction stream. The VAX architecture provides a rich selection of memory operand specifiers, which often require computations to create the address. In a RISC processor, only load and store instructions access main memory.

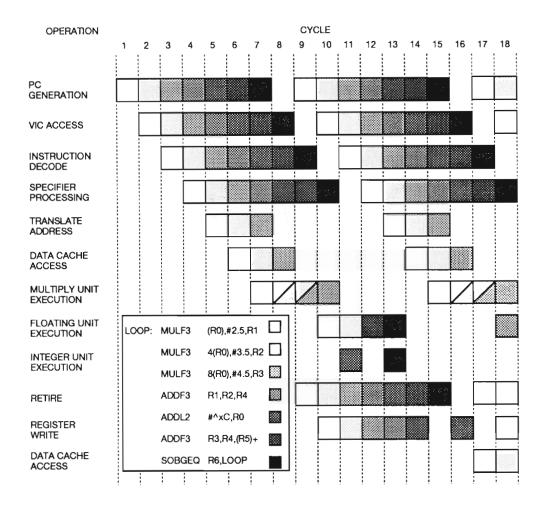

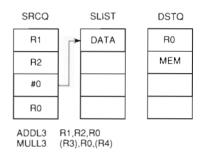

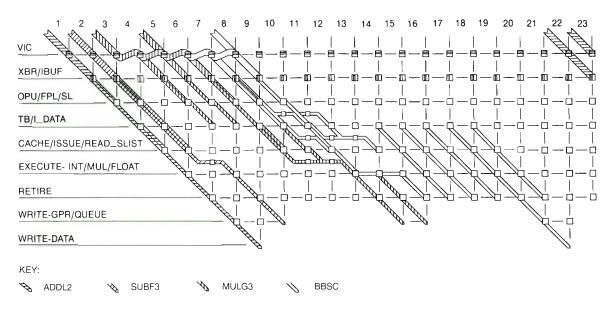

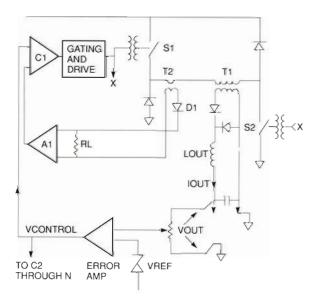

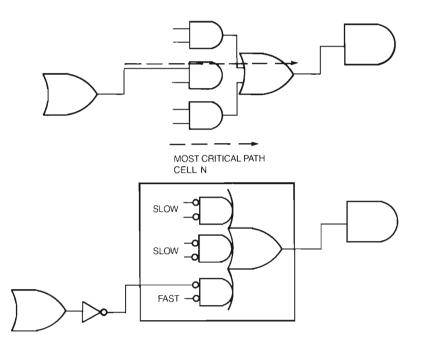

The instruction preprocessing stage (I-box) decodes instructions and fetches operands in the VAX 9000 system. In the execution stage (E-box), simple VAX instructions resemble RISC instructions. A simple opcode describes the operation, a single register file provides source operands, and a destination queue supplies a result descriptor. The I-box operates in parallel as with the E-box, which functions as a RISC processor by executing one instruction each cycle. Execution occurs without the need to identify the operand's source or addressing complexity. Figure 3 illustrates how simple instructions flow through the VAX 9000 pipeline. Although all VAX implementations perform these tasks, the VAX 9000 implementation uses separate, independent hardware units to overlap the work because concurrent operation is a prerequisite for single-cycle instruction execution.

#### Instruction Cache

We used an instruction cache in the I-box to decrease instruction stream fetch latency and reduce the bandwidth requirements on the main cache. Choosing a virtually addressed cache further reduced latency and simplified the design by removing the need for duplicate translation buffers. The virtual instruction cache is an 8 kilobyte (KB) cache with a quadword line size, 32-byte blocks, and a single-cycle access time. Line valid bits are maintained to allow variable size fills from the main data cache. Because the average VAX code block size is 16 to 20 bytes, the block size of the virtual instruction cache provides a good balance between the instruction decode stage and the main cache. Context switches, translation buffer changes, and instruction stream modifications all require that the virtual instruction cache be invalidated. Two complete sets of block valid bits reduce cache sweeps to a single cycle, if consecutive sweeps do not occur within 256 cycles of each other. Block size and frequent sweeping reduce the virtual instruction cache's hit rate to approximately 96 percent, but by filling through the main cache, the miss penalty is minimized.

#### Instruction Decode

Because the majority of instructions executed require only a single cycle to execute, the instruction decode's task of keeping ahead of the E-box is not simple. Most instructions must be decoded in a single cycle to keep the VAX 9000 system's ticksper-instruction (tpi) low.

For example, VAX instructions may contain up to six operand specifiers. With 59 different specifier addressing modes, instruction lengths can vary from a single byte to more than 50 bytes. However, the overall average VAX instruction length is 3.8 bytes, and 98 percent of instructions require only 8 or less bytes.<sup>5</sup> Furthermore, 96 percent of VAX instructions executed use only 3 or less specifiers.

In each machine cycle, a 9-byte instruction buffer is presented to the decode stage (XBAR). The instruction buffer contains instruction stream data prefetched from the virtual instruction cache. Instruction decoding consists of generating an initial microaddress, determining the number of specifiers for the instruction, including each specifier access mode and data type, and forwarding the appropriate specifier data to the operand processing stages. The XBAR can handle up to three specifiers. Instructions that contain more than three specifiers require additional decode cycles. Since general-purpose register specifiers occur approximately 41 percent of the time, three register specifiers can be processed concurrently.6 Short literals comprise nearly 16 percent of the specifiers. However, the XBAR can only decode a single short literal per cycle. The remaining specifiers must all be processed by the operand processing unit, which

| Table 1 Decode Cycles Required |

|--------------------------------|

|--------------------------------|

|        | Instruction                        | VAX-11/780 | VAX 8650 | VAX 9000 |

|--------|------------------------------------|------------|----------|----------|

| MULF3  | R3,R5,R7                           | 3          | 2        | 1        |

| ADDL3  | S <sup>4</sup> #48,R4,@(R2) + [R3] | 5          | 4        | 1        |

| AOBLEQ | S <sup>A</sup> #63,R10,10\$        | 3          | 3        | 1        |

Figure 3 The VAX 9000 Instruction Pipeline

decodes a single complex specifier per cycle. Unlike preceding processors, the XBAR handles multiple specifiers in any order. Table 1 shows the number of decode cycles required for several VAX processors.

#### **Operand Prefetching**

Because most simple instructions are decoded and executed in a single cycle by various pipeline stages, instruction operands also must be handled in a single cycle. Multiple, specialized operand units increase operand processing throughput. From one to three register operands may be forwarded to the E-box by one register unit per cycle. A dedicated short literal unit expands all VAX data formats. The operand processing unit performs complex address calculations and requests memory operand data from the cache unit (M-box). Both the operand processing and short literal units can perform multiple cycle operations.

#### Load/Store Architecture

Load/store architectures separate memory accesses from computation. Loads can be scheduled to place arriving memory data at a functional unit just as an operation begins. To achieve this effect with VAX instructions, memory specifiers are treated as load/ store instructions. VAX memory specifiers describe the effective addresses of memory operands. VAX memory specifiers do not contain the source and destination registers that are specified in RISC load/ store instructions. Rather, the VAX 9000 system assigns temporary register file locations to buffer memory data. By processing specifiers early in the pipeline, data can be scheduled to arrive at the appropriate time.

Memory specifiers act as independent instructions executed in the operand processing unit. This unit creates the operand's effective address and forwards it to the M-box. For loads, the actual memory data is returned to the E-box register file. The translated physical address is saved in a queue of write addresses for store/destination specifiers. When execution results arrive from the E-box, the previously saved address is used to write the data into the cache.

#### Conflict Detection and Resolution

Macropipelining in the VAX 9000 system relies on autonomous units operating in parallel. Each independent unit is optimized for an individual task. However, macropipelining does require that mechanisms be added to resolve data dependencies among instruction processing units. Data conflicts occur when an instruction's results are required by an earlier pipeline stage. An addressing data conflict appears in the following example:

MOVL R0,R1 MOVB TABLE(R1),R2

Any dedicated address calculating hardware must wait for the MOVL instruction results before performing the MOVB instruction's effective address computation. A memory conflict is another form of data dependency.

In the following example,

MOVB R0,(R1) MOVB (R2),R3

a prefetch unit could read the second instruction's source operand while the E-box writes the first instruction's results, if the values of registers R1 and R2 are different. However, when the registers contain identical values, the read must be delayed until the write occurs. The VAX 9000 system uses several different mechanisms to detect and resolve data dependencies. Passing pointers, scoreboard masks within the I-box, the write queue in the M-box, and architectural restrictions are all used to handle various conflicts.

*Register Conflicts* The simplest hardware mechanism employed in the VAX 9000 system is the use of pointers to reference data. The operand processing unit oversees a 16-entry source queue, an 8-entry destination queue, and a 16-entry source list. A single pointer is inserted into the source queue for each source specifier. The pointer represents either a register number, in the case of general-purpose register operands, or a tag that indicates an entry in the source list where the operand data is located. A pointer is added to the destination queue for each destination. This pointer represents a register num-

ber or a flag which indicates that the result should be written to memory.

The instruction issue unit removes source pointers from the source queue. These pointers are used to address either the general-purpose registers or source list for the actual source data. Destination pointers from the destination queue determine where results should be written. Register conflicts can be detected by comparing the source pointers needed to issue an instruction with all issued destination pointers in the destination queue. For example, in Figure 4, the MULL3's R0 source queue entry would match the ADDL3's R0 destination queue entry. A write to the general-purpose registers by the E-box removes the destination queue entry, and the instruction issue can resume.

Figure 4 Register Conflict Detection

To resolve addressing data Addressing Conflicts conflicts, the I-box maintains a read/write register scoreboard. Two register masks are created for each instruction decoded. The first register mask denotes the general-purpose registers that the E-box will read for the instruction, and the second register mask specifies the general-purpose register writes. Each bit in these register masks refers to a single VAX general-purpose register. Specifiers that are being processed in the operand processing unit are checked against up to six previous instruction masks. From the first example above, the specifier [TABLE(R1)] requires that the operand processing unit read R1. If the R1 bit is asserted in any preceding instruction's scoreboard write masks, this effective address calculation must be deferred.

The VAX architecture presents a unique addressing conflict problem because some specifiers, such as -(Rn) and (Rn)+, modify general-purpose registers.

In the following example,

SUBL2 R0,R1 ADDL2 (R0)+,R2 the (R0)+ specifier modifies the contents of R0. Therefore, the operand processing unit cannot update the general-purpose register without affecting the prior instruction. The read masks are used to detect this type of conflict. All specifiers that modify general-purpose registers must check the scoreboard read masks before proceeding with the instruction. Thus, when a conflict occurs, the general-purpose register modification stalls.

When an instruction completes execution, the instruction's read/write mask is removed from the scoreboard. In all addressing conflicts, specifier processing continues once the blocking mask is removed.

Memory Conflicts The write queue is used to resolve memory conflicts. Physical addresses, received from the translation buffer, are inserted into an eight-entry FIFO. These addresses are later paired with the proper write data from the E-box and written into the M-box. To avoid prefetching stale data, all memory addresses for source memory operands are translated and compared with the addresses in the write queue. When no address conflict occurs, the data from memory is forwarded to the source list. Operand requests that conflict with a pending write address are stalled until the conflict is resolved. The conflict is resolved when the appropriate write data is received. The conflicting address is then removed from the write queue.

*Miscellaneous Conflicts* The VAX architecture includes instructions with operands that either are not known when the instruction is decoded (e.g., INSQUE, MTPR), or modify large portions of memory (e.g., MOVC5). To avoid conflicts from these instructions, the I-box suspends processing memory specifiers until the instruction execution is completed. Self-modifying code presents another form of conflict, which is solved by an REI instruction that notifies the hardware of this condition.

#### Branch Instructions

Branch instructions have a substantial influence on the overall performance of a VAX processor. On average, a VAX processor executes 3.9 instructions, including the branch, before a branch starts a new instruction sequence. Instructions that modify the program counter represent nearly 40 percent of the total instructions executed. The VAX 9000 system uses a 1024-entry branch cache and a two-tiered prediction scheme to increase the average code block size and reduce the branch-taken latency. Unlike its predecessors, the VAX 9000 system commits all its resources to a single branch path. The prediction hardware selects the path of execution to resolve memory conflicts for those branch instructions that are decoded before results are available. This path selection is based on prior history, if the branch hits in the branch cache. If the branch does not hit in the branch cache, the path is predicted staticly, based on the instruction's opcode. When the branch executes, the prediction is compared to the actual results. The pipeline is flushed back to the correct code path if the branch prediction was incorrect.

The entries in the branch cache store the branch results of the previous execution of the branch and the target address, if the branch was taken. Because the branch cache is a one-way associative cache that can store only 1024 entries, the results have an average hit rate of approximately 80 percent. However, correct predictions occur 85 percent of the time from the cache, as opposed to an average hit rate of 56 percent, when the predictions are based solely on opcode. Loop branches are always predicted as taken, which increases the overall correct prediction rate to close to 89 percent. By caching branch targets, the calculation may be avoided and a latency factor of one-cycle branch taken is achieved. The branch cache can store a sufficient amount of branch context to eliminate the need to sweep the cache.

The I-box can process instructions with up to two conditional branches outstanding. Unconditional branches (e.g., BSBW, BRB) are processed as ordinary instructions by simply changing the instruction flow. To reduce the penalty for a bad prediction, which results in a four-cycle penalty, operand specifiers that modify general-purpose registers are not processed under a branch prediction and cause the operand processing unit to stall. Also, branch instruction execution is overlapped with the previous instruction to provide the actual branch results earlier.

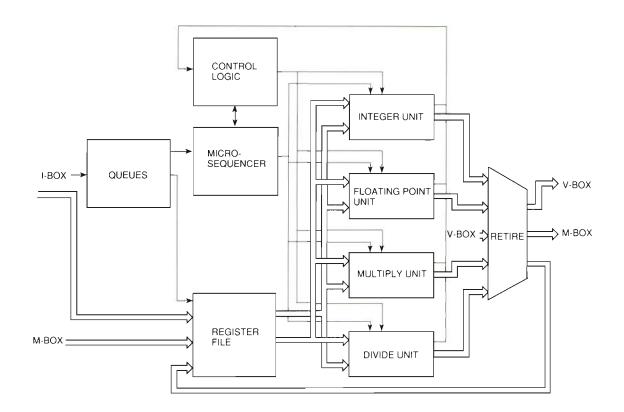

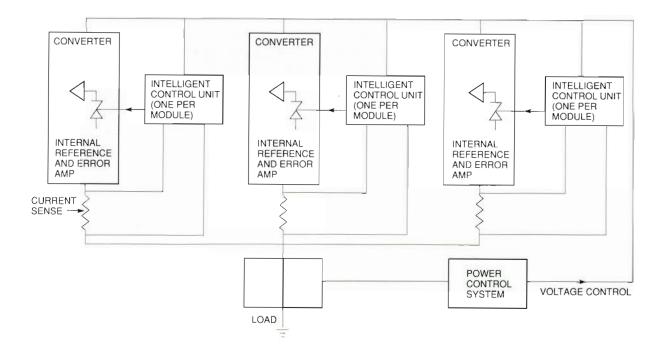

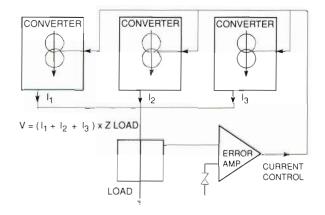

#### Compute-intensive Instructions

Compute-intensive instructions require multiple execution stage cycles. Common examples of these instructions are multiplication, division, and floating point operations. All VAX implementations employ dedicated logic for compute-intensive instructions that occur frequently. Less frequently used instructions depend on microcode-controlled arithmetic and logical data paths. The VAX 9000 system contains four independent execution processors. The integer, floating point, multiply, and divide units execute the VAX instruction set. The I-box preprocesses instructions, which allows instruction execution to overlap in these units. In each cycle, a new instruction can be initiated in the appropriate unit prior to the completion of previous instructions. The floating point and multiply units are pipelined and can accept one instruction each cycle. The integer unit is pipelined for simple instructions. However, complex instructions must use microcode control to perform multicycle operations.

Pipelined instructions are issued in order and proceed through the data path without further microcode control. Upon completion, instruction results are retired in the same instruction order. The instructions must be processed in order because the result of one operation is often needed in a subsequent operation. Therefore, the pipelines must be short and contain data bypasses to make results available quickly. The multiply, float, and divide units' internal data paths are 64-bits wide. To understand how the pipelined and overlapped operations apply to the following operation,

$$y(i) = y(i) + C(i)$$

consider the program:

LODP: MULG3 R6,(R0)+,R4 MULG3 R6,(R0)+,R2 ADDG2 R4,(R1)+ ADDG2 R2,(R1)+

The two MULG3/ADDG2 instruction pairs prevent a pipeline stall that could occur because of data dependencies. The instructions further reduce the loop overhead, which is already fairly small because the loop control instruction was predicted correctly. Instructions and source operands are prefetched. The multiply and add units accept the instructions as they become available. The memory references are made as the operand processing unit processes memory specifiers. The majority of specifier processing is performed independently of the instruction execution.

#### Memory-intensive Instructions

Some VAX instruction classes are primarily memory operations that require only minor computation. Typical examples of these instructions are character string, decimal, and privileged operating system. Pipelined execution offers little advantage to memory-intensive instructions because the number of memory references is not reduced as the number of cycles required for execution is reduced by new implementations. Because memory bandwidth is critical, the VAX 9000 system provides features to benefit these instructions.

For example, the virtual instruction cache services most instruction stream references, which frees the main cache to service prefetched operand references. Both the virtual instruction cache and the main cache have 64-bit data paths, important for character string operations and extended precision arithmetic. The caches are fully pipelined and allow one read per cycle. The main cache block size is 64 bytes, exploiting spatial locality. When cache references do miss, data is wrapped and the most critical data is returned first. A write back, write allocation algorithm further reduces main memory and cache bandwidth requirements and reduces latency.

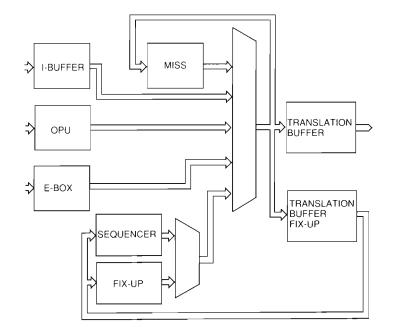

The VAX system is a virtual memory architecture. Virtual addresses need to be translated to physical addresses through page tables in memory. A translation buffer caches the most recently used page tables entries. VAX systems, such as the VAX-11/780 system, process translation buffer misses in microcode, which can be time-consuming. However, the VAX 9000 system uses a memory management processor to process translation buffer misses as part of instruction preprocessing. This operation is performed early in the pipeline and is faster than microcode.

The CALL and RETURN instructions push and pop registers on the stack, and these instructions can be memory-bound. The VAX 9000 system contains both the control logic and the bandwidth to process these registers at a rate of one per cycle.

#### Unconventional Instructions

Special, dedicated hardware was added to the VAX 9000 system to process those VAX instructions that did not fit into the categories listed above. The additional hardware operates within the pipeline architecture and cycle time, and the cost of adding the hardware was minimal.

In the following example,

MOVL R0,-(SP) <----> PUSHL R0

the MOVL and PUSHL instructions perform identical operations, but the PUSHL instruction does not explicitly specify a destination address. On previous VAX systems, the instruction prefetching would stall until the current instruction execution was completed. However, the VAX 9000 modifies such instructions during the decode stage by adding the implied specifiers. The benefits of this enhancement are more evident in the following instructions.

BSBW 10\$ <-----> MDVAL Return\_PC,-(SP) RSB <-----> JMP @(SP)+

Similarly, instructions such as LOCC and CMPC3 implicitly reference the general-purpose registers. The instruction decode stage creates a read/write mask with these references, which allows instruction prefetching to continue.

To aid handling instructions like PUSHR and CALL, the integer execution unit contains special bit mask manipulation hardware, which optimizes general-purpose register saves and restores. The VAX instruction set contains variable-length, bit-field instructions that handle non-byte data. These instructions can reference memory within a 512 megabyte (MB) range. The field referenced is within the first 8 bytes of the base address more than 95 percent of the time. Therefore, to allow instruction prefetching to continue, the operand processing unit assumes that the field is within the initial guadword and requests that data. If, during execution, the field destination actually resides outside the prefetched quadword, the correct data is fetched and the pipeline is flushed to avoid potential memory conflicts.

#### Integrating Vector Processing

The VAX 9000 project team was instrumental in integrating vector operations and data types into the VAX architecture. For many scientific applications, the use of vectors improves performance in three ways:

- Vector instructions specify many operations in a single opcode, which eliminates instruction stream decode as a processing bottleneck.

- Vector registers increase available local storage.

- Vector registers support high peak performance through high bandwidth and short access latency.

The VAX vector architecture implements a load/ store architecture, which permits the hardware to deal with large pieces of memory in a uniform manner and increases the use of parallelism.

We added the vector instructions and data types to the VAX architecture in an integrated fashion. Scalar and vector instructions are mixed throughout the pipelines. Systems that do not include vector processors emulate vector instructions with software, a technique especially useful for program development.<sup>78</sup>

#### Logical Integration

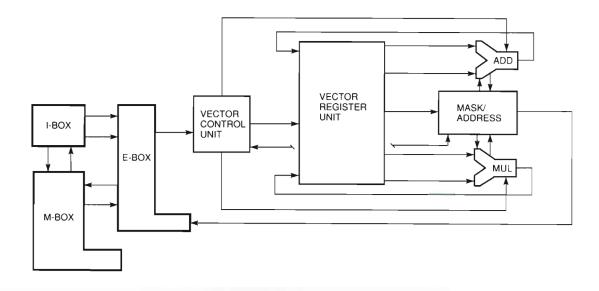

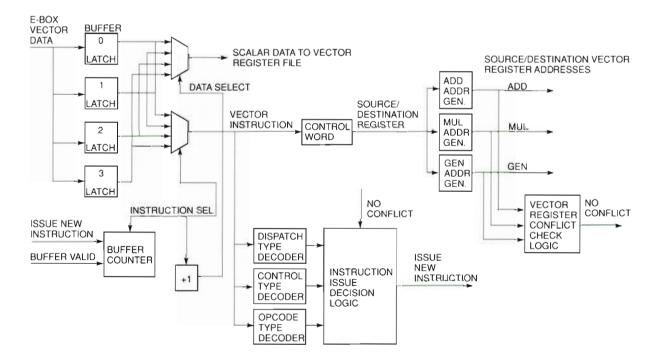

The VAX 9000 vector processor connects to the scalar CPU as an additional functional execution unit. Vector instructions are processed, and operands are stored, in queues, the same as are scalar instructions. As instructions are issued, a control word is sent with instruction operands to the vector processor. The processor contains vector registers and arithmetic units. Addresses for load, store, gather, and scatter operations are also generated by the vector processor. Vector data is stored in the main cache, and both the scalar and vector processors have fast, shared access to that data.

#### Physical Integration

The VAX 9000 scalar and vector processors reside on a single planar board. Three multichip unit slots are reserved for the optional vector processor, which is field-installable. The integration of the vector processor directly with the scalar processor keeps critical interconnects short and reduces vector instruction overhead.

#### **Error Handling**

Reliability, availability, and integrity are critical factors in a high-performance computer system. These factors are affected by the quality of the physical design (i.e., worst-case design), effective cooling, redundant power supplies, and quality controls during manufacture. Still, failures are possible, and the VAX 9000 design had to deal effectively with errors.

Error handling in the VAX 9000 system has two main goals:

- Minimize system service disruption from individual failures

- Maximize the failure information collected for use in preventive and corrective maintenance

A large percentage of hardware failures are intermittent, and many solid hardware failures start as intermittent. The VAX 9000 system was designed to recover from these failures and to use the failure data to predict (and prevent) future problems.

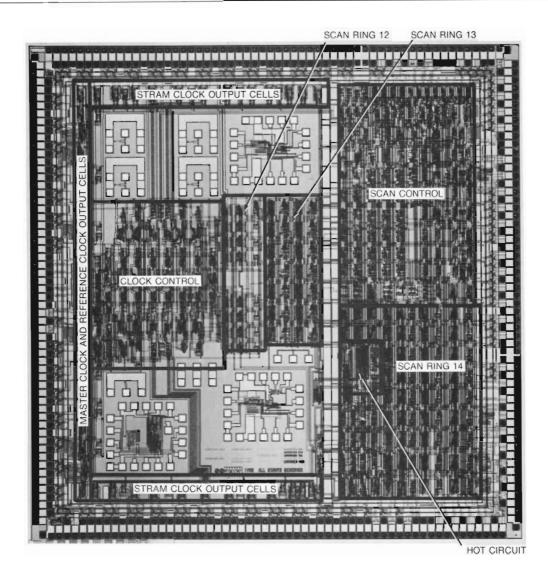

To gather information effectively, VAX 9000 storage elements (i.e., latches, flip flops, and RAM cells) are visible to the service processor unit through a serial diagnostic bus. Most state information that is relevant to isolate the failing component is available for error analysis programs that can be run at a convenient time. The result of this processing is then used to isolate the failing components for quick repair. To access the storage elements through the visibility chain, the system clocks must be disabled, which disrupts the system operation for a period of time. The error may also have affected the execution of the instructions in the pipeline. Error handling minimizes these disruptions by making them invisible to the users almost all the time.

The macroinstruction is the unit of execution in a program that is visible to the user. Between instructions, the program state is clearly defined in terms of memory contents and register values. Interrupts and exceptions are handled between instructions to save this state in an orderly fashion. It is important to handle errors the same way.

Two problems arose in trying to provide the same method of error handling. First, instructions go through many stages in a pipelined computer, and several instructions will be in progress at the same time. It is difficult to identify a beginning and end for each instruction. Second, even when boundaries are established, errors can occur at any time and the errors do not automatically line up with instruction boundaries.

To solve this, we made the E-box the point of synchronization between error handling and instruction execution. In the instruction execution model, the E-box accepts operands, then computes and delivers results for storage. If an error occurs that directly affects one of these steps, the error is synchronous to the execution of that instruction. Asynchronous errors do not directly affect any of these steps and are treated as interrupts, i.e., processed after the E-box completes an instruction but before it starts another instruction.

A synchronous error causes a trap to occur in the E-box when the E-box requests data from the subsystem with the error. Since such data can be unavailable as a result of virtual access problems, the E-box is ready to deal with exceptions at that time, and errors can use the same pipelined mechanism.

We do not differentiate between those synchronous errors that affect computation in the E-box and those that do not. Instead, if the program visible state of the machine has not been modified, the instruction is backed up to the beginning and restarted. Performing this task is not a problem, since the state is normally not changed until the result is stored at the end of the instruction. Errors occurring in early pipeline stages are easily recoverable. In a few cases, memory and registers could have been modified early and, as a result, be affected by the error. Status flags indicate if this has happened. By getting to an instruction boundary, the clocks can be stopped in an orderly fashion, and the state can be read out, including temporary data to be used for failure analysis. The machine can be reset to start processing at the instruction boundary once the clocks are started again.

While the clock is stopped, the CPU cannot interact with other subsystems or I/O processors. To keep these functions from being blocked and possibly timing out, we only stop the clock to the CPU in error, not all the clocks in the system. We also sweep the cache of written data before the clock is stopped, and I/O interrupts are directed to other CPUs in a symmetric multiprocessing system.

#### **Performance Modeling**

When multiple features are added to a CPU design to individually enhance performance, some of those features can interact negatively with each other to decrease performance. Therefore, we designed a performance model to help us evaluate the performance of the design and make trade-offs where necessary. Although instructions were not executed on the model, it is an accurate cycle-bycycle model of the system for most instruction operations. Equally important, the model was written at a high level, which made it easy to modify and use to experiment with different features before they were added to the design.

#### Cycle Time

A perennial CPU design issue is the trade-off between cycle time and cycles per instructions. In a VAX system, the cycle time is often limited by the RAM speed in the control store and cache. We modeled a machine at 8 ns and one at 16 ns for the VAX 9000 system. At 8 ns, the pipelines became longer. Although the peak throughput almost doubled, the model showed that the net performance gain did not offset the risks associated with the shorter cycle time.

#### I-stream Synchronization

The VAX architecture requires that changes to the instruction stream be synchronized with an REI instruction. This synchronization makes it easier to implement an instruction cache that is separate from the main cache. To synchronize, either all memory writes can be watched or the I-cache can be cleared on every REI. The first alternative entails high hardware costs, and the second can affect performance. However, the model showed us that the performance impact would be minimal if the I-cache was refilled from the main cache rather than from main memory because the critical parameters were the main cache bandwidth and the I-cache invalidation time, rather than the refill latency.

#### **Branch Prediction**

The branch prediction scheme used in the VAX 9000 system was analyzed in great detail. We investigated the use of multiple history bits to improve the effectiveness of branch prediction. In all cases, the use of extra bits provided less than a 1 percent improvement in system performance. Furthermore, no multiple bit scheme could be implemented without increasing cycle time because multiple history bit branch prediction schemes update status each time a branch is encountered. Therefore, we chose to use a singlebit technique in the VAX 9000 design. Unlike multiple bit schemes that read and write history bits for each branch instruction encountered, the singlebit technique updates the history bit only when the prediction is wrong. The single-bit scheme is both faster and simpler.

#### Cache Parameters

The main data cache was accurately modeled. The VAX 9000 system uses a first-in first-out (FIFO) block replacement scheme. The performance model predicted that a true least recently used replacement policy would provide an insignificant improvement in performance over the FIFO method. Also, a true least recently used policy requires that status be read and written for each cache access. In contrast, the FIFO replacement policy updates status only when a cache miss has occurred. Further, the update can be done in parallel with the writing of data into the cache block. Although the 128-byte cache block provided a better cache hit, we chose the 64-byte block because it produced better system level performance.

We chose two-set associativity because the model clearly indicated that performance would degrade with a direct-mapped scheme. The model also predicted that a four-way set associative cache would not improve performance enough to justify the extra hardware, design complexity, and cycle time penalty.

The data bypass mechanism, the write queue, and the parallel translation buffer fix-up mechanisms were implemented after the performance model indicated significant performance gains would be achieved from these features.

We also used the performance model as a verification tool. The model provided us with early warnings when a feature did not function in the model, or when the cycle count differed from the count in the gate-level simulation. For example, from the model, we became aware of problems in the design of how conflicts between instructions in specifier processing were handled. Periodically, we compared the performance model to the logical model. Both models were subjected to the same instruction sequences. Deviations of more than ±5.0 percent were investigated. Some design bugs were found that did not affect the results of the program but which did keep performance features from working properly. The average deviation was on the order of  $\pm 1.0$  percent.

Performance tests are among the first programs run on a functional prototype. The VAX 9000 system performed almost as expected. Table 2 compares the actual performance of a VAX 9000 system to its predicted performance for a small sample of modeled programs. The accuracy of the predictions highlights the increasing importance of models in the modern engineering process.

#### Table 2 Performance Measurements of a VAX 9000 System

| Program Name | Predicted (VUPs*) | Measured<br>(VUPs*) |

|--------------|-------------------|---------------------|

| HANOI        | 28.54             | 25.53               |

| FFT45        | 36.87             | 37.85               |

| GAUSS        | 32.72             | 32.57               |

| WHETS        | 27.78             | 27.17               |

| WHETD        | 34.48             | 34.89               |

|              |                   |                     |

Performance measured in VAX units of performance (VUP), where the performance of the VAX-11/780 system = 1.0 VUP.

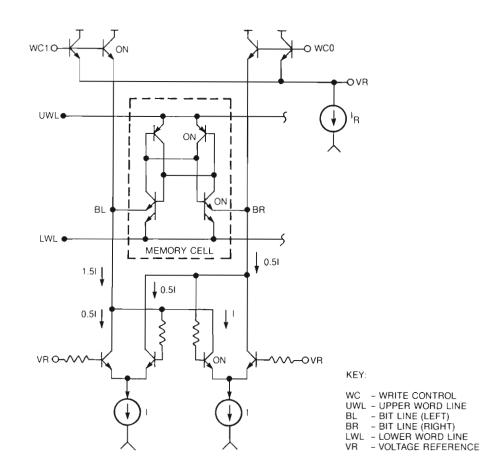

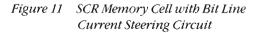

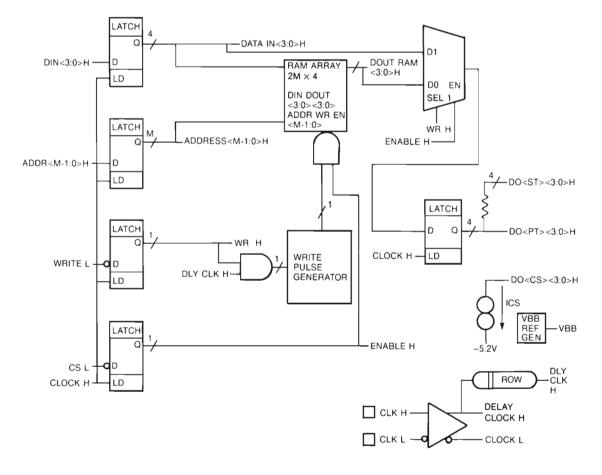

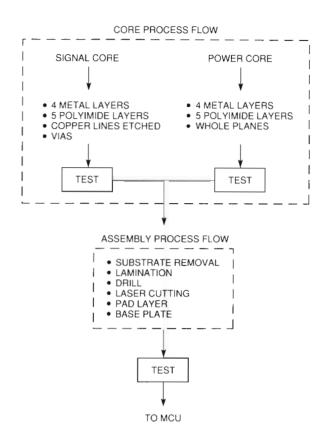

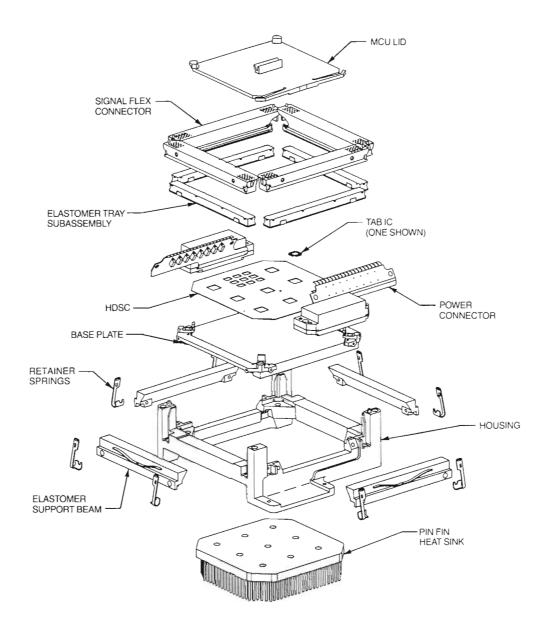

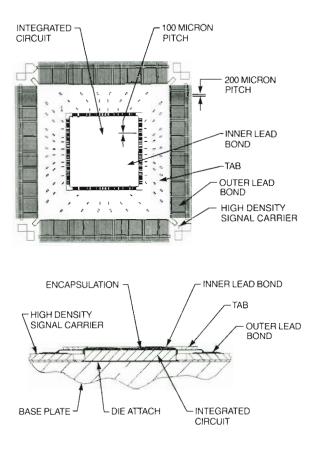

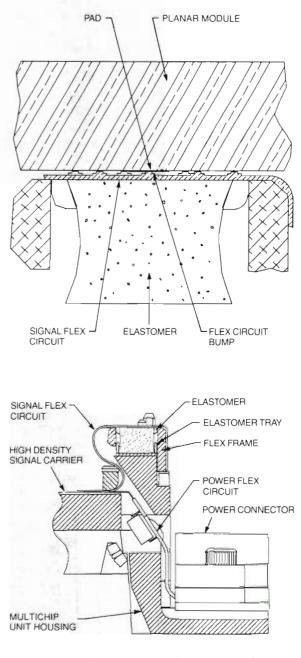

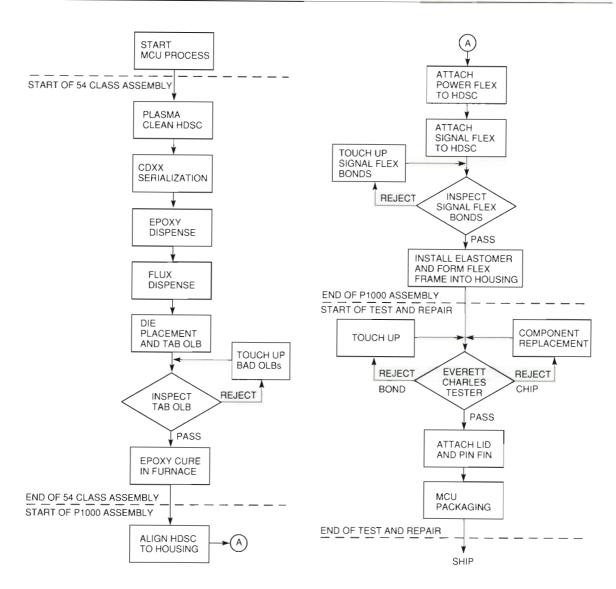

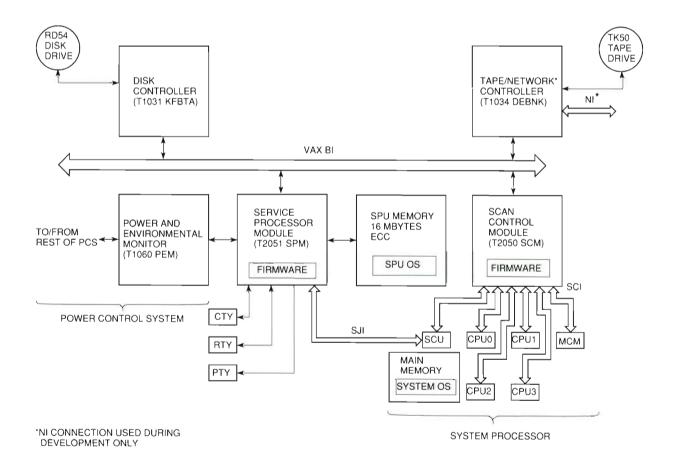

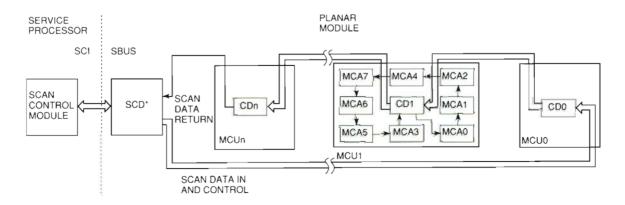

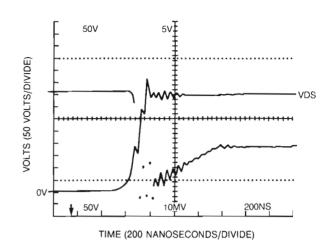

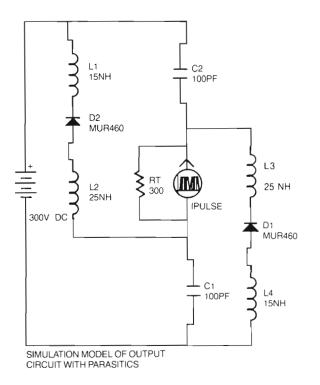

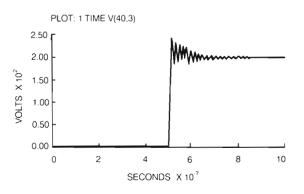

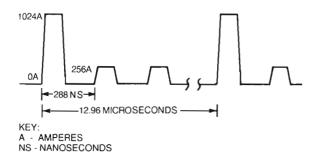

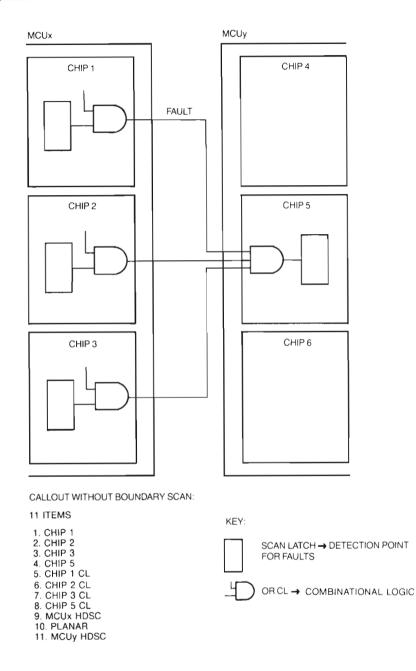

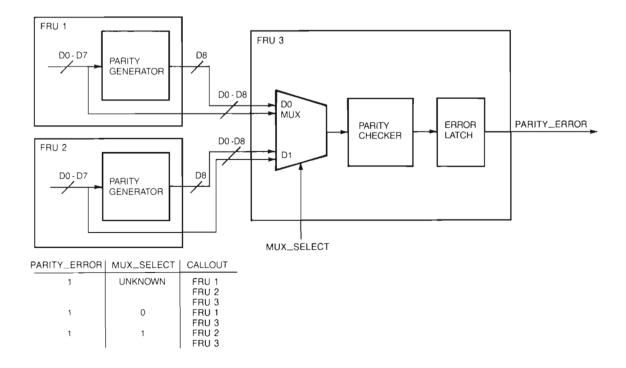

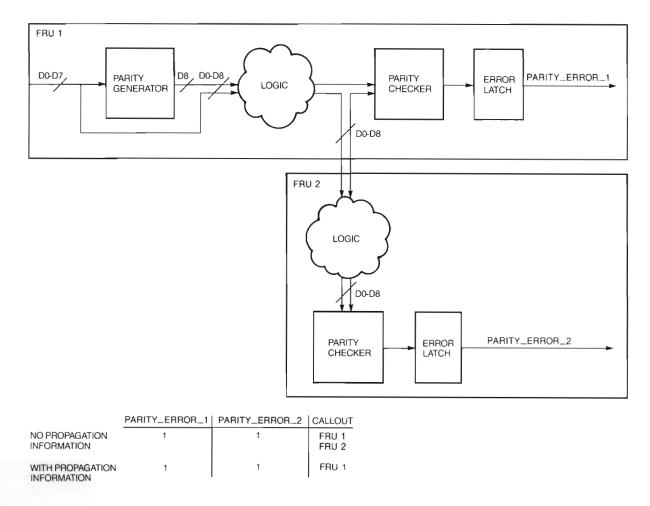

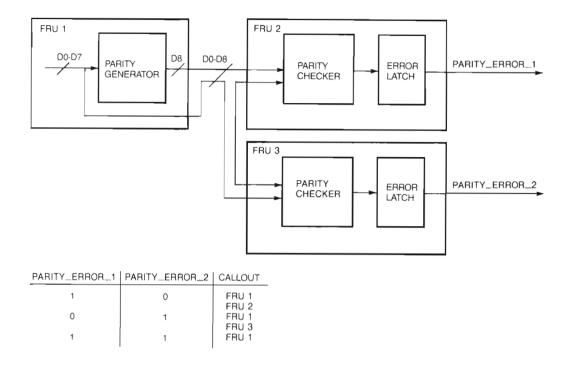

#### Vector Performance